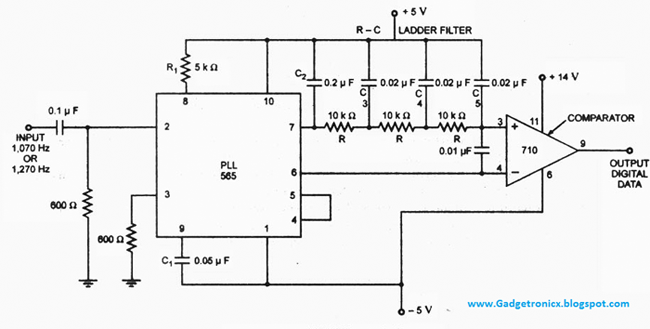

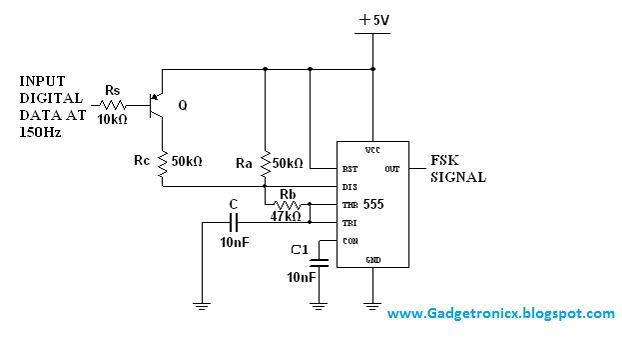

FSK demodulator using PLL 565 circuit helps us to generate FSK signal at ease with minimal components.You have seen how to generate FSK signal using IC 555 in previous posts see the FSK modulator using IC 555.In PLL 565 the frequency shift is usually accomplished by driving a Voltage Controlled Oscillator with the received binary data signal.Thus the output of this demodulator circuit correspond to the input logic 0 or 1 signals.The working of this circuit was discussed briefly below.

WORKING:

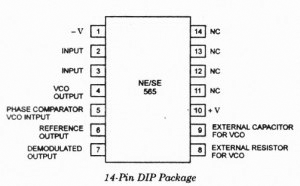

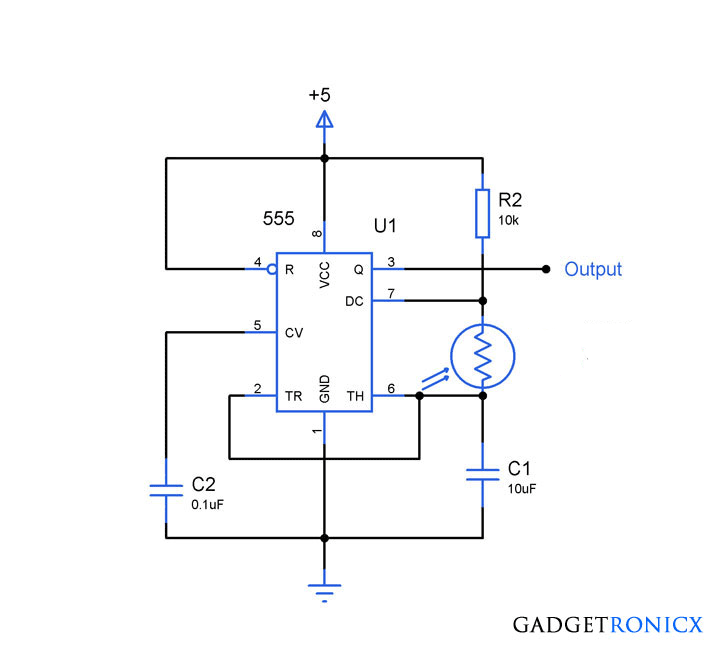

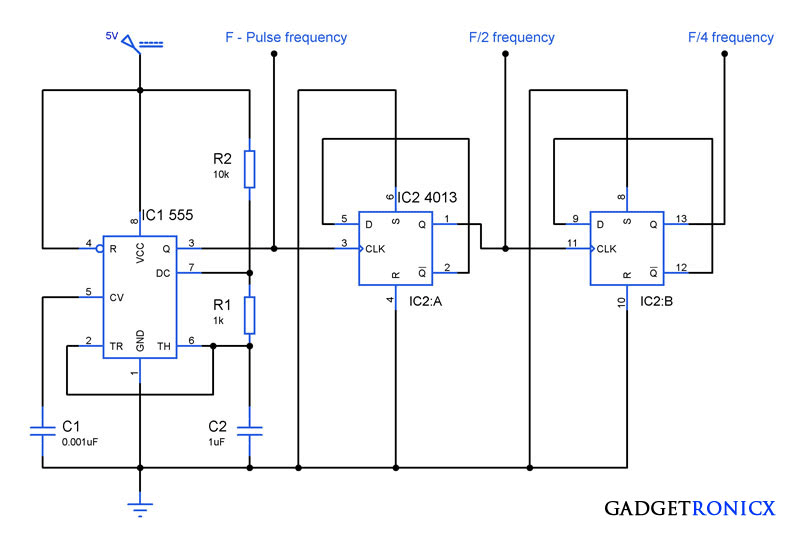

The working of this PLL takes in such a way it locks the input signal frequency and tracks it between the two possible frequencies with a DC shift at the output of this IC.The resistor R1 and C1 determine the free-running frequency of the internal VCO of the PLL IC.You can see the functions of various pin in the below diagram.The VCO comparator output was fed into the Phase comparator input to perform the locking operation of signal frequencies.

A three stage RC filter was used in the circuit for removing the total sum frequency component from the output signal of the IC.The R1 was selected in such a way to adjust the VCO frequency to equalize the voltages obtained at pin 6 and pin 7.The digitized output will obtain high voltage level if the input frequency is low that is output will be high (14 V) when the input frequency is 1070 HZ.The output will be driven to low state (-5V) if the input frequency was 1,270 HZ.

will this work for frequencies other than 1.07and 1.27khz

What is the maximum error-free bitrate for this demodullator ?

Moutaman,

I apologize for my delayed response. The maximum error free bit rate is 1.2kbps.